# Performance of OCTO Layout Style on SOI MOSFET Switches under High-temperature Operation

Egon Henrique Salerno Galembeck<sup>1</sup>, Denis Flandre<sup>2</sup>, Christian Renaux<sup>2</sup> and Salvador Pinillos Gimenez<sup>1</sup>

<sup>1</sup>Electrical Engineering Department, Centro Universitário FEI, São Bernardo do Campo, Brazil <sup>2</sup>Université catholique de Louvain: ICTEAM/ELEN, Louvain-la-Neuve, Belgium e-mail: egonhsg10@hotmail.com, sgimenez@fei.edu.br

Abstract—The present paper performs an experimental comparative study of the main switching electrical parameters and figures of merit of the octagonal layout style for the planar Silicon-On-Insulator (SOI) Metal-Oxide-Semiconductor (MOS) Field Effect Transistors (MOSFET), named Octo SOI MOSFET (OSM), in comparison with the typical rectangular one, regarding a large range of temperature, varying from 300 K to 573 K. The devices were manufactured in a 2 µm fullydepleted SOI (CMOS) technology and are n-type. The results have shown that the OSM is capable of keeping active the Longitudinal Corner Effect (LCE), PArallel Connection of **MOSFETs with Different Channel Lengths Effect (PAMDLE)** and Deactivate the Parasitic MOSFETs of the Bird's Beak Regions Effect (DEPAMBBRE), which are intrinsic effects of the gate octagonal structure of the MOSFET. Besides, it is able to present a higher electrical performance as compared to its rectangular SOI MOSFET (RSM) counterpart (same channel width and bias conditions). As an illustration, the OSM on-state drain current  $\left(I_{ON}\right)$  and off-state drain current  $\left(I_{OFF}\right)$  are respectively 186% higher and 64% smaller as compared to those found in its RSM counterpart.

*Index Terms*— New layout styles; Octo layout style; high-temperature environment; LCE, DEPAMBBRE and PAMDLE effects.

# I. INTRODUCTION

Electronics face great challenges in order to be able to operate in harsh environments (high-temperature, ionizing radiation, etc.), aiming at the reduction of the short channel effects by taking into account the MOSFETs scaling, the decrease of the drain leakage current ( $I_{LEAK}$ ) and power consumption, the diminution of the variations of mobilities of mobile charge carriers in the channel, etc. [1-3].

Several areas of the industry need new electronic systems that must operate reliably under such harsh environments. For example, the exploration and monitoring of the oil, gas and geothermal wells use probes that are sent deep into bore holes, with temperatures reaching 473 K to 573 K (200 °C to 300 °C). Other applications include instrumentation for engines, engine control and condition monitoring systems, power conditioning and control systems for space platforms and satellites, nuclear reactor instrumentation and control, as well as automotive and aeronautics electronics and integrated sensors [1-4].

Many factors determine the practical upper temperature limit of semiconductor devices that does not reflect the inherent temperature limit of the semiconductor materials. The practical limit is frequently determined by the electrical properties of the used semiconductor materials, the interconnections and packaging, both for active devices and passive components [3, 4]. As an indication of the practical upper limit, Bulk Complementary Metal-Oxide-Semiconductor (CMOS) integrated circuits (ICs) have long been offered commercially for operations reaching a maximum of 423 K (150 °C). Temperature up to 473 K-493 K (200-220 °C) can be reached with specific Bulk CMOS process and circuit designs [1, 2].

Other technologies have then been studied to improve the performance of electronic systems operating at high temperatures, such as Fin Field-Effect Transistors (FinFET) built in Silicon-on-Insulator (SOI) processes which have demonstrated a good electrical performance at high temperatures thanks to their gate double structure [5, 6]. Besides, the use of Gate-All-Around (GAA) MOSFET devices in digital CMOS ICs is able to keep the silicon layer fully depleted at extremely high-temperatures [7].

For temperatures above 573 K (300 °C) and, theoretically, up to 873 K (600 °C), silicon carbide (SiC) attracted the attention of the researchers due to its unique electrical and thermo-physical properties. It has a wide bandgap energy (2.2 eV to 3.3 eV, depending on the polytype of SiC), a significantly higher thermal conductivity for thermal management of high-power devices, a high critical breakdown electric field for large power output, a reduced I<sub>LEAK</sub> in MOSFETs, etc. [3, 8-10].

The technology based on 4H-SiC semiconductors utilizes the unique physical and electrical properties of this electrical material to achieve improved performance in high-power and high-temperature electronic circuits [11]. Their complexity nevertheless remains limited due to the lesser integration density and scalability reached in SiC processes as compared to the Si CMOS [11].

The Silicon-On-Insulator (SOI) CMOS technology presents an excellent behavior at high temperatures. When operated in a temperature range from 398 K (125 °C) to 573 K (300 °C), the devices implemented in SOI CMOS technology presents three major advantages as compared to conventional Bulk MOSFETs: the first is the suppression of latch-up; the second is the reduction of  $I_{LEAK}$  and the third, a smaller variation of threshold voltage (V<sub>TH</sub>) with the temperature [2, 12, 13]. Besides, the devices manufactured with SOI CMOS technology further enables high scaling, integration density and production levels. Consequently, this technology has been chosen in this study [2, 12, 13].

Therefore, by mixing the best electrical characteristics of SOI MOSFETs at elevated temperatures and by applying the PN junctions engineering among the source/channel/drain regions or simply gate layout changing of MOSFETs, it is possible to insert novel effects that are capable of improving their electric performances. These new effects are: LCE, PAMDLE, DEPAMBBRE [14-19] that are able to boost its electrical performance. Some examples of this approach are the Diamond [14-22], Octo [23-27], Ellipsoidal [28] and Fish [29] layout styles for MOSFETs, which are capable of

reaching these challenging goals.

The Octo layout style for MOSFETs was specially invented in order to further boost the Electrostatic Discharge (ESD) tolerance and increase the breakdown voltage ( $BV_{DS}$ ) as compared to those one found in the Diamond (hexagonal gate shape) layout style. The same effects found (LCE, PAMDLE and DEPAMBBRE) in the Diamond SOI MOSFET also exist in the OSM structure, in which the LCE in the OSM structure is more pronounced, because in this case, it is possible to find a higher resultant longitudinal electric field (LEF). This can be justified due to the presence of three longitudinal electric field components instead two of the Diamond SOI MOSFET [21-27].

Several references about the Octagonal SOI MOSFET (OSM) describe its better performance in terms of saturation drain current ( $I_{DS}$ ), transconductance (gm), gm/ $I_{DS}$  ratio, voltage gain (A<sub>V</sub>), unit voltage gain frequency ( $f_T$ ),  $R_{ON}$ ,  $I_{LEAK}$ ,  $I_{ON}$ ,  $I_{OFF}$  and  $I_{ON}/I_{OFF}$  ratio, as compared to those observed in the rectangular SOI MOSFET (RSM) counterparts, regarding the same gate areas ( $A_G$ ) and bias conditions in room-temperature environments [14-27].

Four prior experimental studies describe in detail the better electrical performance of the DSM [14, 30] and OSM [31, 32], mainly regarding analog CMOS ICs applications operating at high-temperature environment, in relation to the traditional rectangular MOSFET counterpart.

Within this context, this manuscript aims at studying the electrical performance of the main parameters and figures of merit ( $I_{ON}$ ,  $I_{OFF}$ ,  $I_{ON}/I_{OFF}$  Ratio and On-State Resistance ( $R_{ON}$ )) of the Octo layout style (OLS) for n-type SOI MOSFET switches in relation to the rectangular counterpart in a large range of temperature varying from 300 K to 573 K (27 °C to 300 °C), regarding the same channel width (W) and bias conditions.

# II. DEVICE'S CHARACTERISTICS AND STRUCTURES

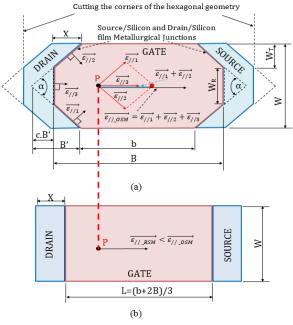

Fig. 1 illustrates the top views of the OSM (Fig. 1.a) and its corresponding RSM (Fig. 1.b), regarding the same channel width and A<sub>G</sub>. In Fig. 1.a, W is the channel width, B and b are the largest and smallest channel lengths, respectively, B' is the height of the triangle part of the hexagonal gate geometry, W<sub>T</sub> is the height of the trapezoidal part that composes the octagonal gate shape which is equal to  $\left(\frac{B-b}{2}\right) \tan\left(\frac{\alpha}{2}\right)$ ,  $W_R$  is equal to (W-2W\_T), which is the channel width of the rectangular part that composes its gate octagonal geometry,  $\alpha$  is the angle formed by the triangular part of the hexagonal geometry of the gate octagonal region, X means the lengths of the drain/source regions, the resultant LEF at the point P of the OSM due to the drain bias  $(V_{DS})$  is  $\overrightarrow{\epsilon_{// OSM}}$ , which is given by the vectorial sum of three LEF components,  $\overline{\epsilon_{//1}}$ ,  $\overline{\epsilon_{//2}}$  and  $\overline{\epsilon_{//3}}$  (LCE effect) that are perpendicular to the interfaces composed by the drain/source and the silicon film regions [21, 26], L is the RSM channel length and the  $\overline{\epsilon_{//RSM}}$  is the LEF of the RSM (only one LEF component).

Considering the point P in these two transistors (Fig. 1), the OSM provides a higher longitudinal electric field  $(\overline{\epsilon_{//_{OSM}}})$  than the one found in the RSM counterpart

$(\overline{\epsilon_{//\_RSM}})$  due to the LCE effect, regarding the same A<sub>G</sub>, W and bias conditions. The OSM structure is created when we cut the extreme corners of the diamond SOI MOSFET by a factor "c" (Fig. 1.a) in order to improve the LCE, the electrostatic discharge (ESD) robustness, increase the BV<sub>DS</sub> and the I<sub>DS</sub> [23-25].

Fig.1 Top schematic views of the OSM (a) and its RSM counterpart (b), regarding the same gate, W and its corresponding longitudinal electric field components.

The channel length (L) of an RSM must be equal to  $\left(\frac{2B+b}{3}\right)$  in order for it to have the same gate area of an OSM. The effective channel length (L<sub>eff</sub>) of an OSM, due to the PAMDLE effect, is given by Equation (1) [24]:

$$L_{eff} = \frac{1}{\left(\frac{1-c}{B-b}\right)ln\left(\frac{B}{b}\right) + \frac{c}{B}}$$

(1)

Regarding the same gate areas of the OSM and RSM, the OSM  $L_{eff}$  is smaller than the RSM L [24]. Therefore, the octagonal layout style for MOSFETs is capable to present a higher  $I_{DS}$  than the one observed in the RSM equivalent, regarding the same bias conditions [19].

The novel effects (LCE, PAMDLE and DEPAMBBRE) take place simultaneously in the OSM and they are responsible for uplifting its electrical performance in relation to the its RSM counterpart [19].

The dimensional characteristics of the OSM and their RSM counterparts used to perform the experimental work are indicated in Table I and all devices present the same channel width equal to  $30 \ \mu m$ .

The parameters studied in this paper have been normalized by the aspect ratio (W/L) in order to avoid the influence of the difference of the devices' dimensions (Table I). The channel length (L\*) of the OSM used to perform the normalizations of the electrical parameters and figures of merit is given by the equation  $L^* = \left(\frac{2B+b}{3}\right)$ , which corresponds to an L of an RSM counterpart which presents the same gate area than the one found in the OSM.

|                                                                                   |              | · ·  | uni unu o | . /   |       |      |

|-----------------------------------------------------------------------------------|--------------|------|-----------|-------|-------|------|

|                                                                                   | SOI nMOSFETs |      |           |       |       |      |

|                                                                                   | OSM1         | RSM1 | OSM2      | RSM2  | OSM3  | RSM3 |

| α(°)                                                                              | 53.1         | -    | 90.0      | -     | 126.9 | -    |

| B (μm)                                                                            | 50.0         | -    | 27.5      | -     | 16.5  | -    |

| L*(µm)                                                                            | 35.0         | -    | 20.0      | -     | 12.7  | -    |

| L <sub>eff</sub> (µm)<br>(PAMDLE)                                                 | 23.0         | -    | 15.20     | -     | 10.75 | -    |

| (W/L) <sub>OSM</sub>                                                              | 0.86         | -    | 1.5       | -     | 2.37  | -    |

| Dimension<br>of PN<br>junction<br>between<br>drain and<br>channel<br>regions (µm) | 57.8         | 30.0 | 39.3      | 30.0  | 32.7  | 30.0 |

| (W/L) <sub>RSM</sub>                                                              | -            | 1.09 | -         | 1.85  | -     | 2.78 |

| L (µm)                                                                            | -            | 27.5 | -         | 16.25 | -     | 10.8 |

| $A_G (\mu m^2)$                                                                   | 994          | 825  | 572       | 487.5 | 363   | 324  |

Table I. Dimensions of the devices used for this experimental study (W=30  $\mu m$  and b=5  $\mu m$ ).

We have used three pairs of SOI MOSFETs as follows:

• An OSM ( $\alpha$ =53.1°), named OSM1, and its RSM equivalent (RSM1). The OSM L\* is equal to 35 µm, which corresponds to L\* =  $\left(\frac{2B+b}{3}\right)$  of an RSM counterpart, with the same gate area of the OSM. However, the OSM L<sub>eff</sub> [Equation (1)] is 14% smaller (PAMDLE Effect) than the one found in the RSM counterpart.

• An OSM ( $\alpha$ =90.0°), named OSM2, and its RSM equivalent (RSM2). The OSM L\* is equal to 20 µm, which corresponds to L of an RSM counterpart, with the same gate area of the OSM. However, the OSM L<sub>eff</sub> is 7% smaller (PAMDLE Effect) than the one in the RSM counterpart.

• An OSM ( $\alpha$ =126.9°), named OSM3, and its RSM equivalent (RSM3). The OSM L\* is equal to 12.7  $\mu$ m, which corresponds to L of an RSM counterpart which presents the same gate area of the OSM. Note that its OSM L<sub>eff</sub> is practically the same from the RSM counterpart, because in this case the PAMDLE effect is practically trivial.

The SOI **MOSFETs** were manufactured in Microelectronics Laboratory of the Université Catholique de Louvain, Belgium. The fully-depleted SOI CMOS manufacturing process used was of 2 µm, notably optimized for high-temperature operation and analog applications at voltages higher than 3 V. The main technological parameters of these SOI MOSFETs are: the gate oxide thickness  $(t_{ox})$ , the silicon film thickness (tsi), and the buried oxide thickness (t<sub>Box</sub>) are equal to 30 nm, 80 nm and 390 nm, respectively. The concentrations of acceptors impurities in the channel region is  $6 \times 10^{16}$  cm<sup>-3</sup> and the donors impurities in the regions drain and source are equal to  $1 \times 10^{20} \text{ cm}^{-3}$  [31, 32].

# **III. EXPERIMENTAL RESULTS AND DISCUSSION**

This section presents comprehensive analytical and experimental results of the switching electrical parameters and figures of merit, taking into account the high-temperature effects, in a range from 300 K to 573 K. The SOI MOSFETs are of n-type, Fully Depleted (FD) and the bias applied to the back-gate is equal to zero, i.e. the second interface is in depletion.

#### A. On-state drain current $(I_{ON})$

The On-State Drain Current ( $I_{ON}$ ) is defined as the drain current that is measured in the strong inversion region, in which the SOI MOSFET is operating with gate voltage ( $V_{GS}$ ) values greater than  $V_{TH}$  [33].

The high temperatures have a great influence on the MOSFET  $I_{DS}$  and consequently on its  $I_{ON}$ . The mobilities of electrons and holes depend, mainly, on the impurity concentrations and the temperature that the semiconductor is exposed to [2, 34, 35]. The flow of the mobile charge carriers in a semiconductor is limited by scattering mechanisms (lattice scattering and impurity scattering) which strongly reduce their mobilities ( $\mu$ ) depending on the temperature. Thus, as the temperature increases, the thermal agitation increases and, consequently, the mobile charge carriers are further scattered in the lattice, and therefore their mobilities are reduced. This phenomenon leads to the reduction of  $I_{DS}$  in a MOSFET exposed at high temperatures in strong inversion [34, 35].

Besides, the phonon scattering is capable of limiting the mobilities of mobile charge carriers in the channel ( $\mu_{ph}$ ) at high temperatures, knowing that these mobilities are reduced proportionally to T<sup>-m</sup>, with m being typically close to 1.5 regarding a n-type SOI MOSFET [2, 34, 35].

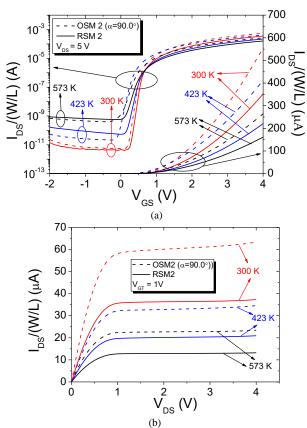

To illustrate the effect that the temperature increase, in a range of the temperature from 300 K to 573 K, causes on the  $I_{DS}$  of a SOI MOSFET, we have presented in Fig. 2.a the experimental curves of  $I_{DS}$  normalized by the aspect ratio (W/L) as a function of  $V_{GS}$  in linear and logarithm scales, regarding  $V_{DS}$  equal to 5 V. Fig. 2.b shows the  $I_{DS}/(W/L)$  as a function of the  $V_{DS}$ , considering the gate voltage overdrive ( $V_{GT}=V_{GS}-V_{TH}$ ) equal to 1 V.

By analyzing Fig. 2, we observe that the  $I_{DS}/(W/L)$ , for all devices, have reduced with the temperature increase, as previously explained [2, 34, 35].

In the triode region (Fig. 2.a), regarding  $V_{GS}$  and  $V_{DS}$  equal to 3 V and 5 V, respectively, the OSM2  $I_{DS}/(W/L)$  presents a gain of 61%, 97% and 66% in relation to  $I_{DS}/(W/L)$  of the its RSM counterpart, regarding the temperature equal to 300 K, 423 K and 523 K, respectively. For the saturation region (Fig. 2.b), regarding  $V_{DS}$  and  $V_{GT}$  equal to 3 V and 1 V, respectively, the OSM2  $I_{DS}/(W/L)$  is always higher (by approximately 67%, 63.8% and 76%, regarding the temperature equal to 300 K, 423 K and 523 K, respectively) than those observed in its RSM counterparts. Therefore, the octagonal layout style for SOI MOSFETs is capable of maintaining the LCE and PAMDLE for high temperatures considered in this experimental study.

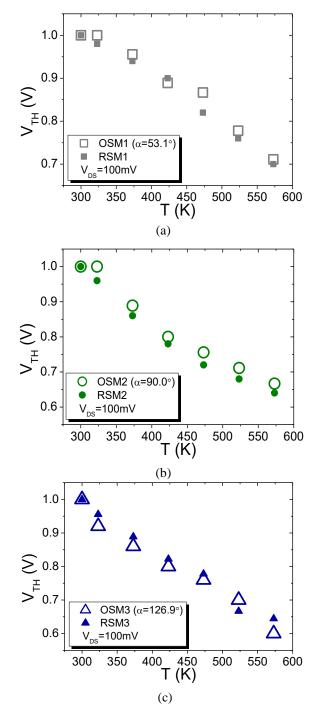

In addition, we have observed that the  $V_{TH}$  of all SOI MOSFETs also vary with increasing temperature. This variation can be observed in Fig. 3, in which the method of extraction of  $V_{TH}$  used was through the maximum peak of the second derivative of the curve  $I_{DS}/(W/L)$  as a function of  $V_{GS}$ , for  $V_{DS}$  equal to 100 mV [2, 34].

By analyzing Fig. 3, we can see that the  $V_{TH}$  of all SOI MOSFETs reduces linearly by about 1 mV/°C, in first approximation, as the temperature increases [34] and therefore the  $I_{ON}$  and  $I_{OFF}$  also are affected by the temperature, because both are strongly influenced by  $V_{TH}$

[34, 36]. But, in this study the variations of  $V_{TH}$  as temperature increases have not influenced the  $I_{ON}/(W/L)$  values, because the  $I_{ON}/(W/L)$  values are extracted as a function of  $V_{GT}$  (the use of  $V_{GT}$  eliminates the differences of the  $V_{TH}$  found in the different MOSFETs).

Fig.2 Experimental curves of the OSM2  $I_{DS}/(W/L)$  and its RSM counterparts as a function of  $V_{GS}$  (a), in linear and logarithm scales and  $V_{DS}$  (b), in which they show the reduction of  $I_{DS}/(W/L)$  with the temperature increase in both devices.

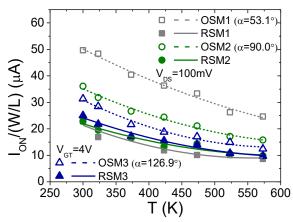

The experimental curves of the  $I_{ON}/(W/L)$  as a function of the temperature (T) of the OSM and their RSM counterparts, regarding  $V_{GT}$  equal to 4 V and  $V_{DS}$  equal to 100 mV in triode region are presented in Fig. 4 (Fig. 2.a shows another example of the variation of  $I_{ON}/(W/L)$  with the temperature).

Fig. 4 shows that the OSM  $I_{ON}/(W/L)$ , with different  $\alpha$  angles, is always higher (by approximately 118%, 58% and 25% for 300 K, and 186%, 60% and 28% for 573 K, regarding  $\alpha$  angles equal to 53.1°, 90.0° and 126.9°, respectively) than the ones observed in their RSM counterparts for all considered temperatures. This can be justified due to the occurrence of LCE, PAMDLE and DEPAMBBRE effects in the OSM structures.

Besides, we can see that LCE, PAMDLE and DEPAMBBRE effects are kept active in high-temperature conditions (up to 573 K). Although, the density of mobile charge carriers in the conduction band increases with temperature, we note that the  $I_{ON}/(W/L)$  of the devices reduces when the temperature increases. This happens mainly due to the reduction of the mobility of mobile charge carriers in the channel region when the temperature increases [2, 34, 35].

Fig.3 Curves of all SOI MOSFET  $V_{TH}$  as a function of temperature, regarding different  $\alpha$  angles of the OSM [53.1° (Fig. 3.a), 90° (Fig. 3.b), and 126.9° (Fig. 3.c)] and their respective RSM counterparts.

When the  $\alpha$  angle of the OSM increases, its gain in the I<sub>ON</sub>/(W/L) decreases due to the reduction of the LCE and PAMDLE effects. Besides, the OSM is increasingly approaching a structure with rectangular gate geometry (RSM).

An interesting fact that the Fig. 4 shows us is that, when normalized by the aspect ratio, the RSM  $I_{ON}/(W/L)$  is similar for the three RSM, contrarily to what occurs in the three OSM, due the effects LCE, PAMDLE and DEPAMBBRE.

Fig.4 Experimental curves of the OSM  $I_{ON}$ (W/L) with three different  $\alpha$  angles and their RSM counterparts as a function of T.

These effects are responsible for boosting the device electrical performances, which are related to the value of the  $\alpha$  angle of the octagonal gate shape of the OSM. Therefore, when the  $\alpha$  angle decreases from 126.9° to 53.1°, for example, these effects are increased in the OSM structure and, consequently, the OSM that presents the smallest  $\alpha$  angle tends to present a higher electrical performance than those that present greater  $\alpha$  angles values. Because of this, the OSM1, with  $\alpha$  angle equal to 53.1°, presents a higher value of I<sub>ON</sub>/(W/L), for all temperatures considered, than those of the OSM2 with a  $\alpha$  equal to 90° and OSM3 with a  $\alpha$  equal to 126.9°, respectively.

Based on these  $I_{ON}/(W/L)$  results of the OSM in relation to their RSM counterparts, the octagonal layout style for SOI MOSFETs can be considered an interesting alternative to be used in digital SOI CMOS ICs applications, either to boost the current drive by fixing the die area of SOI CMOS ICs or to reduce the total die area of analog SOI CMOS ICs, regarding the same current drive [33, 36].

# B. Off-state drain current (I<sub>OFF</sub>)

The  $I_{OFF}$  is given by the MOSFET drain current for  $V_{GS}$  equal to 0 V and  $V_{DS}$  near to the supply voltage ( $V_{DD}$ ). These bias conditions define the MOSFET operating as an open switch. As can be seen in Fig. 2.a, in our case, this drain current is not influenced by the subthreshold slope, but at low  $V_{DS}$ , it is generated in the depletion regions of the reverse-biased PN junctions which are defined by the drain/source and channel regions [34, 37].

A Fully Depleted (FD) SOI MOSFET with the second interface in depletion presents an  $I_{OFF}$  smaller than the one found in the Conventional (Bulk) MOSFET under high temperatures. This happens as the FD SOI MOSFET presents smaller areas of the PN junctions of the drain/source and channel interfaces than those observed in the Bulk MOSFET and due to elimination of large well-to-substrate diffusion leakage. It is important to highlight that  $I_{OFF}$  is considered a leakage drain current in digital SOI CMOS ICs applications [34, 37].

The  $I_{OFF}$  in a SOI MOSFET is, basically, comprised of two components [37]:

I - The generation current in the depleted region of the reverse-biased drain junction ( $I_{\mbox{\scriptsize ger}});$

II - The diffusion current from the undepleted part of the Si film ( $I_{\rm diff}$ ).

The  $I_{ger}$  in the drain region in the n-channel SOI MOSFET can be given by Equation (2) [37]:

$$I_{ger} = q t_{Si} W \frac{n_i}{\tau_g} \left\{ \sqrt{\frac{2 \epsilon_{Si} k T}{q^2 N_A}} \left[ \sqrt{\ln \left(\frac{N_A}{n_i}\right) + \frac{q V_{DS}}{k T}} - \sqrt{\ln \left(\frac{N_A}{n_i}\right)} \right] \right\}$$

(2)

where q is the electron charge,  $t_{Si}$  is the silicon film thickness, W is the device width,  $n_i$  is the intrinsic carrier concentration,  $\tau_g$  is the generation lifetime,  $N_A$  is the channel doping, T is the temperature in Kelvin, k is the Boltzmann constant and  $\epsilon_{Si}$  is the permittivity of silicon [37].

The  $I_{diff}$  in n-channel enhancement-mode SOI MOSFET can be expressed by the Equation (3) [37]:

$$I_{diff} = q W \sqrt{\frac{D_n}{\tau_{rn}}} \left( 1 - e^{-\frac{q V_{DS}}{k T}} \right) \int_0^{t_{Si}} \left( \frac{n_i^2}{N_A} e^{\frac{q \phi(x,T)}{k T}} \right) dx$$

(3)

where  $D_n$  is the electron diffusion constant,  $\tau_{rn}$  is the electron recombination lifetime (equal to  $L_n^2/D_n$ , in which  $L_n$  is the electron diffusion length [33]) and  $\varphi(x,T)$  represents the potential distribution across the film thickness in the undepleted Si film [37].

According to Equation (3), we can note that the  $I_{diff}$  in an SOI MOSFET is determined by the distribution of the potential and by the concentration of minority charge carriers, which vary with the gate bias and the silicon layer thickness (Si). In addition, the concentration of minority charge carriers in the channel region can be reduced by the increase, in modulus, of the back-gate negative voltage in a SOI nMOSFET, thereby reducing the off-state diffusion current and, thus,  $I_{OFF}$  [37].

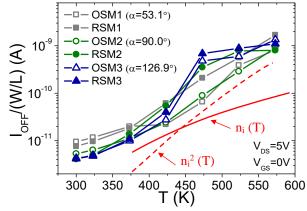

The dependency of the  $I_{OFF}$  with the temperature is related to the intrinsic charge carrier concentration. For temperatures below 423 K and high  $V_{DS}$ , the  $I_{OFF}$  follows the variation of  $n_i$  with the temperature, indicating predominance of the current generation effect [36]. At temperatures above 423 K, the  $I_{OFF}$  follows the variation of  $n_i^2$  with the temperature, suggesting that the diffusion mechanism is dominant [37]. Therefore, the  $I_{OFF}$  increases with the rising temperature.

The  $I_{OFF}$  is a parameter of utmost importance for the SOI CMOS ICs with very low power consumption, when the SOI MOSFETs is operating in the cut-off region [2, 33].

To obtain the I<sub>OFF</sub>, the SOI MOSFET is biased with V<sub>GS</sub> equal to zero and high value of V<sub>DS</sub>, i.e., cutoff region [20] (Fig. 2.a) shows an example of the variation of I<sub>OFF</sub>/(W/L) with the temperature). Fig. 5 illustrates the experimental curves of the I<sub>OFF</sub>/(W/L) as a function of the T of the OSM and their RSM counterparts, for a V<sub>GS</sub> equal to 0 V and a V<sub>DS</sub> equal to 5 V (cutoff region).

Analyzing Fig. 5, the OSM with  $\alpha$  equal to 126.9° and its RSM counterpart present I<sub>OFF</sub> in the same order of magnitude for all temperatures considered. Because, for this angle the octagonal gate geometry of the OSM is very close to the rectangular, resulting in similar values of the PN junctions areas and lengths between the drain and channel depletion regions for both devices.

Fig.5 The experimental  $I_{OFF}/(W/L)$  of the OSM and their RSM counterparts as a function of T, red lines show physical trends.

When the temperature is between 300 K and 373 K, the  $I_{OFF}$  values to the OSM1 and OSM2 can be seen to be slightly higher than those found in the OSM3 and their respective RSM counterparts and to increase with  $\alpha$  reduction. However, above the temperature of 423 K, where the diffusion current is prevailing [36], the I<sub>OFF</sub> of the OSM1 and OSM2 are always lower (approximately 64% and 55% for 423 K, and 53% and 13% for 573 K, with  $\alpha$  angles equal to 53.1° and 90.0°, respectively) than those found in their RSM counterparts, as well as compared to OSM3, considering the same bias conditions.

One hypothesis to explain these results is that, below 373 K the generation  $I_{OFF}$  dominates and is linked to the electrical field in the depletion region which increases in the OSM.

On another hand, at higher temperatures, the diffusion  $I_{OFF}$  is known to be inversely proportional to the diffusion lengths ( $L_n$  and  $L_p$ ), according equation (4) [34] (from the standard PN junction theory).

$$I_{OFF} = A\left(\frac{qD_{n}n_{p0}}{L_{n}} + \frac{qD_{p}p_{n0}}{L_{p}}\right) = Aqn_{1}^{2}\left(\frac{1}{N_{A}}\sqrt{\frac{D_{n}}{\tau_{rn}}} + \frac{1}{N_{D}}\sqrt{\frac{D_{p}}{\tau_{pn}}}\right)$$

(4)

where A is the area of the drain to channel PN junction,  $n_{p0}$  is the equilibrium electron concentration in the p-type region,  $D_p$  is the hole diffusion coefficient,  $p_{n0}$  is the equilibrium hole concentration in the n-type region,  $L_p$  is the hole diffusion length and  $\tau_{pn}$  is the hole recombination lifetime (equal to  $L_p^2/D_p$ ) [34]. As the main effect of the OSM angle reduction is to increase the longitudinal electrical field, it can only impact the diffusion current through second-order effects, such as the reduction of diffusion coefficients through mobility, given by the Einstein Relationship [ $D_n=(kT/q).\mu_n$ ] [34], another possibility could be the balance of the diffusion by a drift current component. This should be studied in details in future works by three-dimensional (3D) numerical simulations.

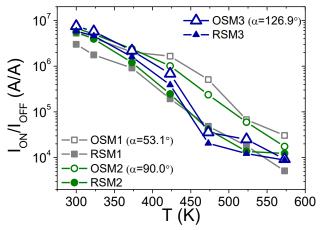

### C. ION/IOFF Ratio

The electrical performance and processing velocity of digital CMOS switches, which operate at high frequencies, is directly related with the  $I_{ON}/I_{OFF}$  ratio [32].

The  $I_{ON}/I_{OFF}$  ratio decreases with the increase of the temperature, because the increase of  $I_{OFF}/(W/L)$  at high

temperatures is more significant (it depends on  $n_i^2$  – Section III.B) than the reduction in  $I_{ON}/(W/L)$  (which depends on  $\mu$  – Section III.A), mainly regarding the values of the temperature above of 423 K.

Fig. 6 illustrates the experimental  $I_{ON}/I_{OFF}$  ratios (in logarithm scale) of the different OSM and their RSM counterparts, as a function of the temperature. The  $I_{ON}$  has been obtained considering the  $V_{GT}$  equal to 4 V and  $V_{DS}$  equal to 100 mV, regarding the transistors operating in the triode region, as a closed switch. The  $I_{OFF}$  has been obtained considering the  $V_{GS}$  equal to 0 V and  $V_{DS}$  equal to 5 V, where we consider the SOI MOSFETs are operating in the cutoff region, as an open switch.

Observing Fig. 7, we can observe that the  $I_{ON}/I_{OFF}$  ratio for OSM1 and OSM2 are always higher (approximately 75% and 22% for 300 K and 492% and 42% for 573 K, where the  $\alpha$  angles are equal to 53.1° and 90.0°, respectively) than those found in their respective RSM counterparts for all temperatures, regarding the same bias conditions.

Fig.6 The  $I_{ON}/I_{OFF}$  ratio of devices as a function of the temperature.

The experimental results of  $I_{ON}/I_{OFF}$  ratios of the OSM are influenced by its higher  $I_{ON}$  values compared to their RSM counterparts (Section III.A) and, mainly, by the reduction of  $I_{OFF}$  with the increase of the temperature in comparison to the  $I_{OFF}$  values presented by their RSM counterparts, as explained in Section III.B. This is another important difference of the octagonal layout style for implementing SOI MOSFET technology in relation to the hexagonal gate geometry [14, 30], because for all temperatures considered, the OSM  $I_{ON}/I_{OFF}$  ratios are always higher to the ones found in their respective RSM counterparts.

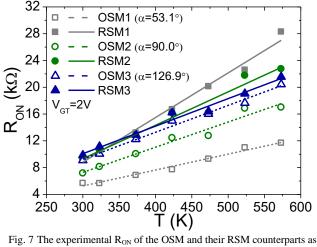

#### D. On-state resistance

The on-state resistance  $(R_{ON})$  is a very important parameter for CMOS switches applications [27]. The smaller its value, the less noise the SOI MOSFET produces. Besides, when the  $R_{ON}$  values are smaller, the MOSFETs achieve higher speeds [38].

The  $R_{ON}$  is determined when the SOI MOSFET operates in the triode region, i.e., when it operates as a closed switch and it is mathematically given by Equation (5) [33, 39]:

$$R_{ON} = \frac{1}{\left[\mu_n C_{OX1} \frac{W}{L} (V_{GS} - V_{TH})\right]}$$

(5)

wherein  $\mu_n$  is the electron mobility and  $C_{OX}$  is the front gate oxide capacitance.

This equation is only valid when  $V_{DS}$  is much smaller than  $V_{GT}$  [20]. We can see by Equation (5) that  $R_{ON}$  is inversely proportional to the mobilities of mobile charge carriers in the channel. Therefore, when T is increasing, the mobility is reducing and consequently  $R_{ON}$  will be increasing in the channel region [2, 34, 35].

Fig. 7 presents the experimental  $R_{ON}$  of the OSM with three different  $\alpha$  angles and their RSM counterparts as a function of T. The experimental  $R_{ON}$  values have been obtained by the ratio between the  $V_{DS}$  variation ( $\Delta V_{DS}$ ) in relation to the  $I_{DS}$  variation ( $\Delta I_{DS}$ ) in linear region of the Triode region, for  $V_{GT}$  equal to 2 V, in this case.

It is possible notice that on-state resistances of the devices increase when T increases. Besides, the OSM  $R_{ON}$  values are always significantly lower (approximately 40%, 24% and 8% for 300 K, and 59%, 25% and 5% for 573 K, regarding  $\alpha$  angles equal to 53.1°, 90.0° and 126.9°, respectively) than those measured in their RSM counterparts. This happens due to the LCE and PAMDLE effects (high I<sub>DS</sub> values - Section III.A), resulting in low values of  $R_{ON}$  and subsequently leading to higher MOSFETs I<sub>DS</sub> values.

The gain provided by the octagonal layout style for MOSFET in  $R_{ON}$  are also discussed in the following references regarding numerical simulations and experimental results in room temperature [24, 25] and radiation environment [40, 41].

a function of T

Making an analogy with the study of reference [28], it possible to predict that the delay time constant ( $\tau = R_{ON}.C_{GS}$ , which  $C_{GS}$  is gate capacitance) of the OSM tends to be smaller than the one found in its RSM counterpart, regarding that both devices present the same W, and bias conditions. This can be proven by reference [28], which has shown that the gate capacitance of an ellipsoidal layout style for MOSFET (EM) is around 11% greater than the one found in its conventional MOSFET (CM) counterpart in room temperature, because its PN junctions length between the drain/source and channel regions are higher, considering both devices with the same W and bias conditions. However, the  $R_{ON}$  of the EM is 65% remarkably smaller than that those found in its CM counterpart, and therefore, the  $\tau$  of the EM is significantly smaller (61%) than the one observed in its CM counterpart in room temperature [28].

Analogously, as the ellipsoidal layout style is an evolution of octagonal layout style, we can consider that the OSM will also have a gate capacitance slightly higher than the one found in its RSM counterpart, because its PN junctions length between the drain/source and channel regions are higher than the one found in its RSM counterpart (Table I). Therefore, thanks to the much smaller OSM R<sub>ON</sub> values in comparison to the one observed in their RSM counterpart, the OSM delay time constant tends to be smaller than their RSM counterpart presents.

CMOS switches are extensively used in power management circuits, for example to turn off (i.e. to put in sleep mode) digital CMOS ICs [42], or in DC-DC converters [43] to generate the low IC supply voltage (e.g. 1-3 V) from the main power supply at higher voltage (typically 3-5 V). To meet efficiency objectives, such techniques require that the MOSFET switches added to the circuit must be upsized, i.e. keeping large aspect ratios (W/L) to deliver the full IC current at low voltage drop when turned on, while limiting the leakage current when turned off with a high drain-source voltage drop. Consequently, the use of MOSFETs with channel lengths (L) larger than the minimum dimension (L<sub>min</sub>) allowed by the CMOS technology must be used. Therefore, the Octo SOI MOSFETs can be considered an alternative device to be used in such techniques because they present effective channel lengths (Leff) larger than the Lmin, while providing higher ION with reduced IOFF when interfacing voltages of 3-5 V for high-temperature applications.

#### **IV. CONCLUSION**

This manuscript has reported that the octagonal layout style implemented for SOI MOSFETs technology is capable of keeping active the LCE, PAMDLE, DEPAMBBRE effects under high temperature operation (from 300 K to 573 K), consequently, notable enhancements in the main switch electrical parameters and figures of merit in comparison than those observed in their RSM counterparts, such as  $I_{ON}$ ,  $R_{ON}$  and I<sub>ON</sub>/I<sub>OFF</sub> ratio. We have described the electrical behavior of the OSM I<sub>OFF</sub>/(W/L) in relation to the its SOI MOSFET counterpart, showing that the Octo layout style for SOI MOSFETs is outstandingly able to reduce the value of the SOI MOSFETs I<sub>OFF</sub> and, consequently, to reduce the power consumption (ecologically-friendly solution) of the CMOS switch applications at high temperature. Moreover, as it is enormously imperative to aggregate the everlasting requirement for energetic efficiency and low cost, this layout technique does not cause any supplementary charge for the current and complex planar CMOS ICs manufacturing process.

#### **ACKNOWLEDGEMENTS**

The authors would like to thank the FAPESP (grant #2017/10718-7), CNPq (grant#308702/2016-6) and CAPES for financial support.

#### REFERENCES

- Colinge, J. P., FinFETs and Other MOSFET Multi-Gate Transistors, Springer, 2008.

- [2] Colinge, J. P., Silicon-On-Insulator Technology: Materials to VLSI, Kluwer Academic Publishers, 2004.

- [3] Zhang, Nuo, Silicon Carbide Bipolar Junction Transistors for High Temperature Sensing Applications, University of California, Berkeley, Technical Report No. UCB/EECS-2016-170, December 1, 2016

- [4] Lu, Guo-Quan, Calata, Jesus N., Lei, Guangyin, Chen, Xu, "Lowtemperature and Pressureless Sintering Technology for Highperformance and High-temperature Interconnection of Semiconductor Devices", 2007 International Conference on Thermal, Mechanical and Multi-Physics Simulation Experiments in Microelectronics and Micro-Systems. EuroSime 2007, 16-18 April 2007, London, UK.

- [5] OLIVEIRA, A. V. et al., "High temperature influence on analog parameters of Bulk and SOI nFinFETs", 2015 Joint International EUROSOI Workshop and International Conference on Ultimate Integration on Silicon (EUROSOI-ULIS), p. 293 – 296, Bologna, 2015

- [6] Diab, A. et al., "Room to High Temperature Measurements of Flexible SOI FinFETs With Sub-20-nm Fins", *IEEE Transactions on Electron Devices*, v. 61, p. 3978 - 3984, December 2014.

- [7] Vandooren, A.; Colinge, J. P.; Flandre, D., "Gate-All-Around OTA's for Rad-Hard and High-Temperature Analog Applications", *IEEE Transactions on Nuclear Science*, v. 46, n. 4, p. 1242-1249, Agosto 1999.

- [8] Lostetter, A. et al., "High-temperature silicon carbide and silicon on insulator based integrated power modules", 2009 IEEE Vehicle Power and Propulsion Conference, 7-10 Sept. 2009, Dearborn, MI, USA.

- [9] Zhou, Weicheng, Zhong, Xueqian, Sheng, Kuang, "High temperature stability evaluation of SiC MOSFETs", 2014 *IEEE 26th International Symposium on Power Semiconductor Devices & IC's (ISPSD)*, 15-19 June 2014, Waikoloa, HI, USA.

- [10] Funaki, Tsuyoshi et al., "Power Conversion with SiC Devices at Extremely High Ambient Temperatures", *IEEE Transactions on Power Electronics*, vol. 22, p. 1321 – 1329, Issue: 4, July 2007.

- [11] Patil, Ganesh C., Wagaj, Santosh C., Ghate, Pravin M., "A simple analytical model of 4H-SiC MOSFET for high temperature circuit simulations", 2014 Annual IEEE India Conference (INDICON), 1-13 December 2014, Pune, India.

- [12] Petrosyants, Konstantin O. et al., "High temperature submicron SOI CMOS technology characterization for analog and digital applications up to 300°C", 2017 33rd Thermal Measurement, Modeling & Management Symposium (SEMI-THERM), 13-17 March 2017, San Jose, CA, USA.

- [13] Kappert, Holger et al., High temperature SOI CMOS technology and circuit realization for applications up to 300°C, 2015 IEEE International Symposium on Circuits and Systems (ISCAS), 24-27 May 2015, Lisbon, Portugal.

- [14] Galembeck, E. H. S., Renaux, C., Flandre, D. and Gimenez, S. P., Experimental Comparative Study Between the Diamond MOSFET and Its Conventional Counterpart in High Temperatures Environment, *in Proceedings IEEE S3S Conference*, vol. 1, p. 1–2, October 2013.

- [15] Gimenez, S. P., "Diamond MOSFET: An innovative layout to improve performance of ICs", *Solid-State Electronics*, v. 54, p. 1690-1699, 2010.

- [16] Gimenez, S. P. and Alati, D. M., "Comparative Exp. Study between Diamond and Conv. MOSFET", *ECS Transactions*, vol. 33(6), p. 121-132, 2010.

- [17] Gimenez, S. P. et. al., "Improving the Protons Radiation-Robustness of Integrated Circuits by Using the Diamond Layout Style", in *Proceedings RADECS (IEEE)*, 2012.

- [18] Gimenez, S. P., Leoni, R. D., Renaux C., Flandre D., "Using diamond layout style to boost MOSFET frequency response of analogue IC", *Electronics Letters*, vol. 50, Issue: 5, p. 398-400, 2014.

- [19] Gimenez, S. P., Layout Techniques for MOSFETs, Morgan & Claypool, 82 p., 2016.

- [20] Gimenez, S. P., Davini, E., Peruzzi, V.V., Renaux, C., Flandre, D., "Compact Diamond MOSFET model accounting for PAMDLE applicable down 150 nm node", *Electronics Letters*, vol. 50, issue: 22, p. 1618-1620, 2014.

- [21] Bellodi, M. and Gimenez, S. P., "Drain Leakage Current Evaluation in the Diamond SOI nMOSFET at High Temperatures", ECS Transactions, vol. 25(3), p. 243-2532009, 2009.

- [22] Liu, X., Dai, L., Li, P., Zou, S., "Electrical performance of 130 nm PD-SOI MOSFET with diamond layout", *Microelectronics Journal*, October 2018.

- [23] Fino, L. N. S., Silveira, M. A. G., Renaux, C., Flandre, D. Gimenez, S. P., "Improving the X-ray radiation tolerance of the analog ICs by using OCTO layout style, *in Proceedings SBMicro 2013*, vol. 1, p. 1-4, Sept. 2013.

- [24] Neto, E. D., Simoen, E., Claeys, C., Gimenez, S.P., "OCTO FinFET", SBMicro 2013, vol. 1, p. 1-4.

- [25] Gimenez, S. P., Alati D. M., "OCTO SOI MOSFET: An Evolution of the Diamond to Be Used in the Analog Integrated Circuits". In: EUROSOI 2011 - VII Workshop of the Thematic Network on Silicon on Insulator Technology, Devices and Circuits, Granada: Universidad de Granada, v. 1, p. 91-92, 2011.

- [26] Fino, L. N. S., Renaux, C., Flandre, D. Gimenez, S. P., "Using OCTO SOI nMOSFET to Reduce Die Area of Analog Integrated Circuits", *Seminatec 2012*, São Bernardo do Campo, v.1, 2012.

- [27] Fino, L. N. S., Renaux, C., Flandre, D. Gimenez, S. P., "Experimental Study of the OCTO SOI nMOSFET to Improve the Device Performance", *EUROSOI 2012 - VIII Workshop of the Thematic*, 2012.

- [28] Gimenez, S. P., Correia, M. M., Member, Neto, E. D., Silva, C. R., "An innovative Ellipsoidal layout style to further boost the electrical performance of MOSFETs", *IEEE Electron Device Letters*, vol. 36, p. 705-707, July 2015).

- [29] Alati, D. M., Simoen E., Claeys Cor, Gimenez S. P., "FISH SOI MOSFET: Modeling, Characterization and Its Application to Improve the Performance of Analog ICs", *Journal of Electrochemical Soc.*, vol. 158, issue 12, p. H1258-H1264, 2011.

- [30] Gimenez, S. P., Galembeck, E. H. S., Renaux, C., Flandre, D., "Diamond layout Style Impact SOI MOSFET in High Temperature Environment", *Microelectronic Reliability*, v. 55, issue 5, p. 783-788, 2015.

- [31] Gimenez, S. P., Galembeck, E. H. S., Flandre, D., "Impact of Using the Octagonal Layout for SOI MOSFETs in a High Temperature Environment", *IEEE Transactions on Device and Materials Reliability*, v. 15, issue 4, p. 626-628, 2015.

- [32] Galembeck, E. H. S., Renaux, C., Flandre, D., Gimenez, S. P., "Boosting the SOI MOSFET Electrical Performance by Using the Octagonal Layout Style in High Temperature Environment", *IEEE Transactions on Device and Materials Reliability*, v. 17, issue 1, p. 221-228, 2017.

- [33] Ravazi, B., Design of Analog CMOS Integrated Circuits, Nova York: Mc Graw Hill, 2001.

- [34] Colinge, J. P., Colinge, C. A., *Physics of Semiconductor Devices*, Kluwer Academic Publishers.

- [35] Wolpert, David, Ampadu, Paul, Managing Temperature Effects in Nanoscale Adaptive Systems, p. 174, ISBN 978-1-4614-0748-5, Springer, 2012.

- [36] Li, Y.; Chou, H.-M, "Comparative Study of Electrical Characteristic on Sub-10-nm Double-Gate MOSFETs", *IEEE Transactions on Nano* technology Electron, v. 4, n. 5, p. 645- 647, September 2005.

- [37] Rudenko, T. et al, "Properties of high-temperature off-state currents in SOI MOSFETs derived from the diffusion mechanism", *High Temperature Electronics*, Berlin, p. 83-86, 1999.

- [38] Sakakibara, J., Urakami, Y., Yamaguchi, H., "Ultra Low On-Resistance Super 3D MOSFET Under 300V Breakdown Voltage", 16<sup>th</sup> International Symposium on Power Semiconductor Devices & ICs, 2004.

- [39] Le Coz, J., et. al., "DTMOS power switch in 28 nm UTBB FD-SOI technology", S3S Conference, p. 1-2, 2013.

- [40] Fino, L. N. S. et. al. "Boosting the total ionizing dose tolerance of digital switches by using OCTO SOI MOSFET", Semiconductor Science and Technology, v. 30, p. 105024-12p, 2015.

- [41] Fino, L. N. S., Silveira, M. A. G., Renaux, C., Flandre, D., Gimenez, S. P., "Total Ionizing Dose Effects on the Digital Performance of Irradiated OCTO and Conventional Fully Depleted SOI MOSFET", RADECS 2013, Oxford.

- [42] D. Bol, V. Kilchytska, J. De Vos, F. Andrieu, and D. Flandre, "Quasidouble gate mode for sleep transistors in UTBB FD SOI low-power high-speed applications," Proc. - *IEEE Int. SOI Conf.*, pp. 1–2, 2012.

- [43] Hiraoka, Y. et al. "Application of the thin-film SOI power MOSFET fabricated by sub-µm-rule CMOS/SOI process for the DC-DC converter", *Proceedings of the 10th International Symposium on Power Semiconductor*, 1998. p. 147-148.